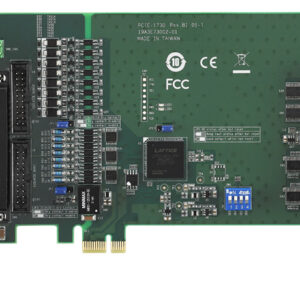

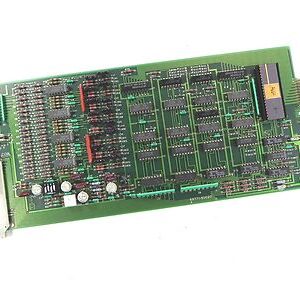

The Acromag IP-EP201 is an Industry Pack (IP) module that delivers 48 TTL bidirectional digital I/O lines through a JTAG-reconfigurable Altera Cyclone II FPGA. Designed for industrial digital interfacing, this module combines user-programmable logic with direct FPGA control and flexible clocking, enabling custom I/O solutions without external interface logic.

– Technical Specifications

FPGA Core

• Altera Cyclone II EP2C20

• JTAG or IP bus configuration download

Digital I/O

• 48 TTL bidirectional I/O lines, 5V tolerant

• LVTTL external clock input connected directly to FPGA global clock pin

• Direction control in 8-channel groups

Clocking

• On-board Cypress CY22150 clock synthesizer (or equivalent)

• Frequency range: 250 kHz to 100 MHz

• IP bus clock support: 8 MHz and 32 MHz

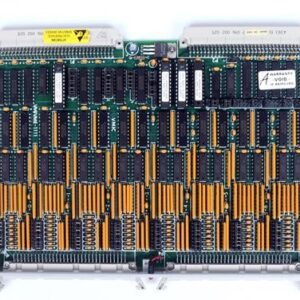

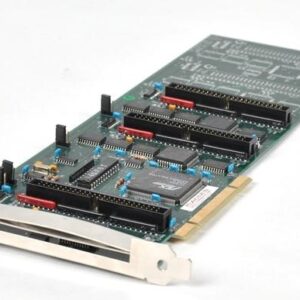

IP Bus Interface

• ANSI/VITA 4-1995 compliant

• 8 or 16-bit I/O space data width

• 8-bit ID space

• Access time (8 MHz): 1 wait state, 375 nS cycle

• Two interrupt request levels

• Wired DMA support (not enabled in example firmware)

Power-Up & Configuration

• On-board CPLD manages boot and FPGA download

• FPGA assumes full IP bus control post-configuration

Environmental

• Operating temperature: 0 to 70°C (standard); -40 to 85°C (IP-EP201E extended range)

• Storage temperature: -55 to 125°C

• Humidity: 5 to 95% non-condensing

– Key Features

• User-programmable logic via Altera Quartus II tools and VHDL

• Rapid I/O reconfiguration without hardware redesign

• Global clock distribution for timing-critical applications

• Independent channel direction control enables mixed input/output configurations

– Typical Applications

Digital signal acquisition, real-time control interfaces, test automation, industrial protocol bridging, and custom instrumentation requiring flexible I/O expansion.

– Compatibility & Integration

Engineering Design Kit includes schematics, parts list, and example VHDL code. Requires VHDL expertise and Altera Quartus II development environment.

Reviews

There are no reviews yet.