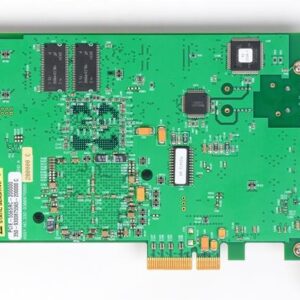

The JTAG Technologies JT3707/TSI DataBlaster is a boundary-scan controller for IEEE 1149.1 testing and in-system programming (ISP). It delivers sustained test clock speeds to 40 MHz with programmable TCK adjustment from 500 Hz to maximum, enabling flexible performance tuning for complex, high-density PCBs. The triple-serial interface (TSI) provides USB 2.0 (480 Mbit/s), USB 1.1 (12 Mbit/s), Ethernet, and FireWire (IEEE-1394-1995 and IEEE-1394A-2000) connectivity at 100, 200, and 400 Mbit/s operation, supporting integration across diverse computing platforms.

## Technical Specifications

**Core Capability:** IEEE 1149.1 boundary-scan testing and in-system flash programming

**Test Clock (TCK):** 40 MHz sustained; programmable from 500 Hz to maximum; automatic speed matching for optimal chain performance

**Connectivity Interfaces:**

• USB 2.0 at 480 Mbit/s and USB 1.1 at 12 Mbit/s

• Ethernet

• FireWire (IEEE-1394-1995 and IEEE-1394A-2000) at 100, 200, and 400 Mbit/s

**TAP Architecture:** Four synchronized test access ports via included JT 2147 QuadPOD system; each TAP pod (JT 2149) features a 20-way TAP connector and eight-pin connector for four static I/O lines

**TAP Voltage Range:** 1.0 V to 3.6 V, individually programmable per TAP

**Flash Memory Buffer:** Expandable up to 128 Mbits

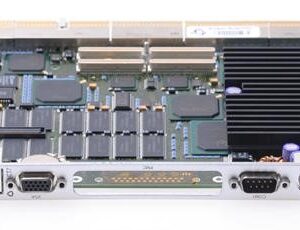

**QuadPOD System (JT 2147):** Bench-top signal conditioning module comprising JT 2148 transceiver and four removable JT 2149 TAP pods, connected via 50-way shielded cable assembly

## Key Features

• Scalable architecture upgradeable to JT3717 with JT 2108 ETT (Enhanced Throughput Technology) module

• Optimized binary file format (BSX) for high-speed execution

• Optional SCIL measurement modules and JT 2149/DAF (Digital/Analog/Frequency) modules for expanded capability

• Full compatibility with existing JTAG Technologies test and ISP files

## Typical Applications

Board testing, CPLD programming, fast in-system flash memory programming, vector-intensive manufacturing test, and engineering environments with small-to-large data block requirements

## Compatibility & Integration

Fully compatible with existing JTAG Technologies test and ISP file libraries. Low-voltage TAP system supports modern embedded and FPGA device ecosystems.

Reviews

There are no reviews yet.