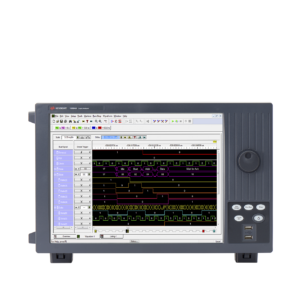

The Keysight 16806A is a 204-channel portable logic analyzer designed for digital system debugging, validation, and signal integrity analysis. It combines deep memory acquisition, multiple timing modes, and advanced triggering capabilities to support complex digital designs from low-speed state analysis through high-speed asynchronous timing measurements. The 15-inch color display and touch-screen option enable flexible lab and field deployment.

– Technical Specifications

Channels & Memory

• 204 maximum channels

• Memory depth: 1 M, 4 M, 16 M, or 32 M vectors per channel (software selectable and upgradeable)

Timing Analysis (Asynchronous)

• Timing Zoom: 4 GHz at 250 ps resolution with 64 K memory depth

• Conventional Timing: 1.0 GHz (1 ns resolution) or 500 MHz (2 ns resolution) with deep memory

• Transitional Timing: 500 MHz

State Analysis (Synchronous)

• Maximum state clock rate: Up to 450 MHz

• Maximum state data rate: Up to 500 Mb/s per channel (250 Mb/s or 500 Mb/s modes)

• Master-to-master clock time: 4 ns (250 Mb/s) or 2 ns (500 Mb/s)

• Sample range: −3.2 ns to +3.2 ns with 80 ps typical adjustment resolution

• Setup and hold time: 0.5 tWidth

Signal & Triggering

• Single-ended signal support with adjustable threshold (−5 V to +5 V in 10 mV increments)

• Eye Finder: Automatic threshold and sample position setup for high-speed bus measurements

• View Scope: Integrated oscilloscope and logic analyzer waveforms in single display

Interfaces

• 10/100 Base-T LAN

• Six USB 2.0 ports (two front, four rear)

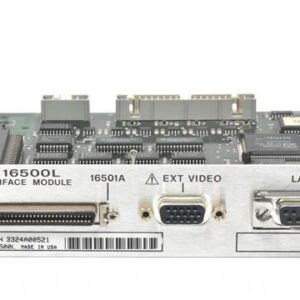

• One PCI and one PCI Express x1 expansion slot

• Trigger In: 5 V Max pk, CAT I isolated

• Clock In: 5.5 V Max pk

• Clock Output: Synchronized with 7 ns delay in 14 steps

System

• 15-inch color display (touch-screen optional)

• Windows XP Professional or Windows 7 (OS dependent on serial number)

• Power: 115/230 Vac ±20%, 48–66 Hz, 775 W Max (auto-detected)

– Key Features

• Deep memory: Up to 32 M vectors per channel for extended capture windows

• Dual-mode sampling: State analysis up to 450 MHz, timing analysis up to 4 GHz

• Precision timing: 250 ps resolution in zoom mode, 2 ns in conventional mode

• Automatic eye detection identifies marginal signals across all channels simultaneously

• Mixed-signal viewing correlates digital timing with analog waveforms

– Typical Applications

• FPGA and ASIC validation during development and production

• High-speed serial and parallel bus analysis

• Embedded system protocol debugging

• Signal integrity and timing margin characterization

• Cross-domain verification (analog/digital correlation)

– Compatibility & Integration

Portable form factor with standard 10/100 LAN and multiple USB ports for quick lab and field connectivity. PCI and PCIe expansion slots enable integration with external modules. Threshold adjustment from −5 V to +5 V supports single-ended logic families across 3.3 V, 2.5 V, and 1.8 V domains.

Reviews

There are no reviews yet.