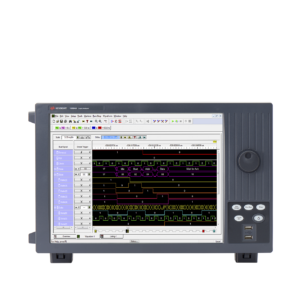

The Tektronix TLA7S08 is a high-performance serial data analyzer module that captures, displays, and analyzes serial data signals with advanced triggering across all protocol layers. Purpose-built for PCI Express Gen 1 and Gen 2 interfaces, this 8/16-channel module delivers 2.5 GSa/sec acquisition speed and supports link widths from x1 to x16. The analyzer employs a powerful trigger state machine spanning Physical, Data Link, and Transaction layers, enabling packet-level, sequence, and error triggering. Hardware filtering extends link capture time while dynamic link width and data rate tracking accommodate real-time protocol changes from 2.5 Gb/s to 5.0 Gb/s. Memory depth reaches 32M 8b/10b symbols per channel, with a minimum differential input amplitude of 120 mV peak-to-peak and input common mode range of ±7.5 V. The compression probing system minimizes circuit intrusion, while support for internal or external reference clocks—with or without spread spectrum clocking modulated 0% to −0.5% at 30–33 kHz—ensures flexible test configurations. Lane number, polarity, and data rate autoset capabilities streamline PCIe protocol recognition and synchronization. Sync to L0s occurs within 12 FTS packets typical. The module installs in Tektronix portable or benchtop logic analyzer mainframes and provides real-time link status indicators for immediate measurement feedback.

– Technical Specifications

• Channels: 8/16 serial analyzer

• Sample Rate: 2.5 GSa/sec

• Memory Depth: 32M 8b/10b symbols per channel

• Acquisition Speeds: 2.5 Gb/s and 5 Gb/s

• Frequency Margining: ±10% at 2.5 Gb/s and 5.0 Gb/s

• Maximum Input Signal to Probe: ±7.5 V

• Minimum Differential Input Amplitude: 120 mV peak-to-peak

• Input Common Mode Range: ±7.5 V

• Minimum Input Eye Height: 60 mV for continuous data streams

• Data Rate Modulation: 0% to −0.5% at 30–33 kHz

• Operating Temperature: +5 °C to +45 °C

– Key Features

• Multi-layer trigger state machine: Physical, Data Link, and Transaction layers

• Packet-level, sequence, and error triggering

• Hardware filtering extends link capture time

• Dynamic link width tracking (x1, x2, x4, x8, x16)

• Bidirectional support for x1 and x4; unidirectional for x8

• Data rate tracking across 2.5–5.0 Gb/s transitions

• Autoset lane number, polarity, and rate with TS1/TS2 recognition

• L0s synchronization within 12 FTS packets typical

• Internal/external reference clock with optional spread spectrum clocking

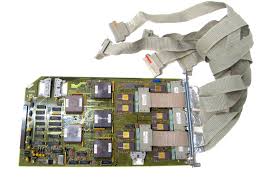

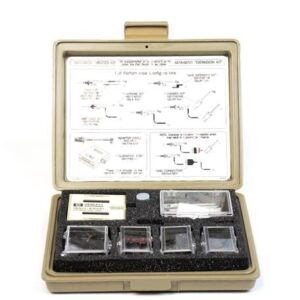

• Compression probing system for minimal circuit loading

• Protocol decode and error reporting in Listing and Waveform views

– Typical Applications

• PCI Express Gen 1 and Gen 2 link validation

• Serial protocol debugging and characterization

• Multi-lane link analysis and margin testing

• Hardware design verification

– Compatibility & Integration

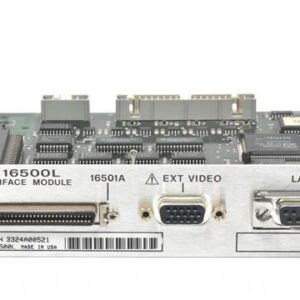

• Installs in Tektronix portable or benchtop logic analyzer mainframes

• Real-time link status indicators

Reviews

There are no reviews yet.